Diferencia entre revisiones de «Paginación»

| (No se muestran 15 ediciones intermedias de 3 usuarios) | |||

| Línea 3: | Línea 3: | ||

La paginación es una estrategia de organización de la memoria física que consiste en dividir la memoria en porciones de igual tamaño. A dichas porciones se las conoce como páginas físicas o marcos. La división de la memoria en páginas facilita la gestión de la memoria física. | La paginación es una estrategia de organización de la memoria física que consiste en dividir la memoria en porciones de igual tamaño. A dichas porciones se las conoce como páginas físicas o marcos. La división de la memoria en páginas facilita la gestión de la memoria física. | ||

| − | Los marcos están | + | Los marcos están identificados por un número, conocido como número de página física. Cada página física se asigna en exclusividad a un proceso. |

| − | A su vez, se dispone de páginas lógicas. Todo proceso tiene su propio espacio de páginas lógicas, cada página lógica está mapeada a un marco. El mapeo entre páginas lógicas y páginas físicas se mantiene en la tabla de páginas. Cada proceso dispone de su propia tabla de páginas. | + | A su vez, se dispone de páginas lógicas. Todo proceso tiene su propio espacio de páginas lógicas, cada página lógica está mapeada a un marco. El mapeo entre páginas lógicas y páginas físicas se mantiene en la tabla de páginas. Cada proceso dispone de su propia tabla de páginas. En tiempo de [[conmutación de procesos]], se restablece la tabla de páginas del proceso que pasa a estado a activo, por tanto, forma parte del contexto de la ejecución del proceso en estado activo. |

| − | Suponiendo que el tamaño de página es de 8 Kbytes (2^13 bytes), en un procesador de 32 bits (4 bytes, 2^2 byte) - se dispone de un total de 2^19 marcos. | + | El proceso dispone de todo el direccionamiento lógico, que puede emplear según sus necesidades. En un procesador de 32 bits, un proceso dispone de 2^32 = 4 GBytes de memoria lógica. Suponiendo que el tamaño de página es de 8 Kbytes (2^13 bytes), en un procesador de 32 bits (4 bytes, 2^2 byte) - se dispone de un total de 2^32 / 2^13 = 2^19 marcos = 524288 marcos. |

| + | |||

| + | El mecanismo de direcciones lógica permite aislar entre sí a los procesos en ejecución, puesto que no conocen la dirección física efectiva en la que se almacenan los datos a los que se hace referencia. | ||

= Funcionamiento = | = Funcionamiento = | ||

| − | + | El traductor de memoria paginada toma la dirección lógica y, por medio de la tabla de página, obtiene la dirección física real. | |

| − | + | Los bits más significativos de una dirección lógica representan el número de página lógica, los menos significativos el desplazamiento dentro de la página. Concretamente, en un procesador de 32 bits, con un tamaño de página de 4 Kbytes = 2^12, se emplean 12 bits para el desplazamiento dentro de la página. Es decir, para referenciar los datos que una página contiene. Los restantes 20 bits más significativos indican el número de página. | |

| − | + | El traductor de memoria paginada es parte de la arquitectura, por tanto, el sistema operativo únicamente tiene que establecer la tabla de páginas del proceso en tiempo de conmutación, de manera que cualquier acceso a una dirección lógica se traduce a una dirección física de una manera transparente al proceso. | |

[[Archivo:Paginas.png]] | [[Archivo:Paginas.png]] | ||

| − | + | Las páginas disponen de mecanismos de protección, expresados en bits de lectura, escritura y ejecución. Lo que permite definir páginas de sólo lectura, por ejemplo, para almacenar constantes. Páginas de sólo lectura y ejecución, para almacenar código, así como páginas de lectura y escritura para el heap (montón) o la pila (stack) del proceso. | |

| + | |||

| + | Si se accede a una página lógica que no existe en la tabla de páginas del proceso, el sistema eleva una excepción que resulta en la finalización de la ejecución del proceso. | ||

= Otras características = | = Otras características = | ||

| − | *Los valores óptimos para las porciones son: en arquitectura de 32 bits es de 4KB, y en arquitectura de 64 bits es de 8KB. | + | * ¿Cuál es el tamaño de página idóneo? Los valores óptimos para las porciones son: en arquitectura de 32 bits es de 4KB, y en arquitectura de 64 bits es de 8KB. |

| − | *Los criterios vistos en | + | |

| + | * Los criterios vistos en la gestión de memoria mediante particiones de tamaño variable no tienen aplicación en la gestión de la memoria paginada, pues todos los huecos disponibles son de igual tamaño. | ||

| + | |||

| + | == Dispositivo de traducción de direcciones paginadas == | ||

| − | + | Podemos almacenar la tabla de páginas en el propio traductor o en memoria principal. | |

| − | |||

| − | |||

*'''Tabla de páginas en el traductor:''' | *'''Tabla de páginas en el traductor:''' | ||

| − | + | El dispositivo de traducción de memoria dispone de una zona en la que se almacena la tabla de páginas. En tiempo de conmutación, se tiene que copiar la tabla de páginas a memoria principal y se restaura la tabla de página del nuevo proceso que pasa a estado activo, lo cual ralentiza el tiempo de conmutación de procesos. Lo que hace que no sea viable en sistemas modernos, en los que se gestionan grandes cantidades de memoria. | |

| − | El dispositivo de traducción | ||

| − | |||

| − | |||

| − | |||

| − | + | *'''Tabla de páginas en memoria principal:''' | |

| − | |||

| − | + | La tabla de página se almacena en la memoria principal, el dispositivo traductor dispone de unos registros que almacenan la dirección de memoria en la que se almacena la tabla de páginas y su tamaño. Debido a que la tabla de páginas está en la memoria principal se necesita, por cada acceso a memoria, un acceso a memoria adicional para obtener el número de página física asociado a la página lógica. Para mantener un tiempo de acceso aceptable se establece una memoria asociativa en el dispositivo de traducción de memoria paginada que conserva la relación página lógica <-> página física utilizadas recientemente. | |

==Tabla de páginas multinivel== | ==Tabla de páginas multinivel== | ||

| Línea 52: | Línea 52: | ||

*'''Tabla de páginas para todo el sistema:''' Es una variante de las tablas de página multinivel, en la que el dispositivo traductor sólo contiene una entrada por cada proceso, indexadas por PID, y una dirección de tabla que contiene las páginas de dicho proceso. Así, ante una conmutación de procesos basta con cambiar de PID. | *'''Tabla de páginas para todo el sistema:''' Es una variante de las tablas de página multinivel, en la que el dispositivo traductor sólo contiene una entrada por cada proceso, indexadas por PID, y una dirección de tabla que contiene las páginas de dicho proceso. Así, ante una conmutación de procesos basta con cambiar de PID. | ||

==Elementos de administración== | ==Elementos de administración== | ||

| − | |||

| − | + | Para mantener la contabilidad de marcos libres se pueden emplear estructuras de datos tales como: | |

| + | |||

| + | *'''Mapa de bits de marcos libres:''' Que contiene 1 si está asignada a un proceso, o 0 si está libre. | ||

| + | *'''Lista de marcos libres:''' Hay una lista global de marcos libres y una lista por proceso de marcos ocupados. | ||

| + | |||

| + | Además, se puede emplear el mecanismo de los compañeros para mantener listas de varias páginas consecutivas (bloques) de tamaño en base a potencia de 2. Por ejemplo, suponiendo un sistema con páginas de 4 Bytes, bloques de 4 Kbytes (orden 0), bloques de 8 Kbytes (orden 1, dos páginas), bloques de 16 Kbytes (orden 2, cuatro páginas), bloques de 32 KBytes (orden 3, 8 páginas) y así sucesivamente. | ||

| + | |||

| + | Una reserva de página de orden 0 nunca falla a no ser que no haya memoria disponible en el sistema. La de orden 1 puede fallar si no hay dos páginas consecutivas. | ||

| − | + | El hecho de asignar páginas de manera consecutiva permite explotar mejor la propiedad de localidad espacial en el acceso a memoria. | |

| − | |||

| − | + | 7.5 [[Sistema_combinado | Sistema combinado]] | |

Revisión actual del 18:40 2 abr 2020

Contenido

Definición

La paginación es una estrategia de organización de la memoria física que consiste en dividir la memoria en porciones de igual tamaño. A dichas porciones se las conoce como páginas físicas o marcos. La división de la memoria en páginas facilita la gestión de la memoria física.

Los marcos están identificados por un número, conocido como número de página física. Cada página física se asigna en exclusividad a un proceso.

A su vez, se dispone de páginas lógicas. Todo proceso tiene su propio espacio de páginas lógicas, cada página lógica está mapeada a un marco. El mapeo entre páginas lógicas y páginas físicas se mantiene en la tabla de páginas. Cada proceso dispone de su propia tabla de páginas. En tiempo de conmutación de procesos, se restablece la tabla de páginas del proceso que pasa a estado a activo, por tanto, forma parte del contexto de la ejecución del proceso en estado activo.

El proceso dispone de todo el direccionamiento lógico, que puede emplear según sus necesidades. En un procesador de 32 bits, un proceso dispone de 2^32 = 4 GBytes de memoria lógica. Suponiendo que el tamaño de página es de 8 Kbytes (2^13 bytes), en un procesador de 32 bits (4 bytes, 2^2 byte) - se dispone de un total de 2^32 / 2^13 = 2^19 marcos = 524288 marcos.

El mecanismo de direcciones lógica permite aislar entre sí a los procesos en ejecución, puesto que no conocen la dirección física efectiva en la que se almacenan los datos a los que se hace referencia.

Funcionamiento

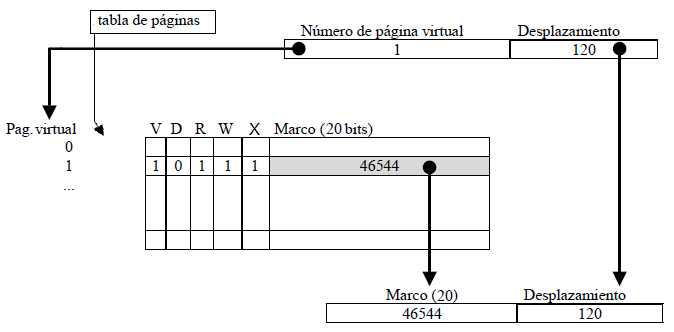

El traductor de memoria paginada toma la dirección lógica y, por medio de la tabla de página, obtiene la dirección física real.

Los bits más significativos de una dirección lógica representan el número de página lógica, los menos significativos el desplazamiento dentro de la página. Concretamente, en un procesador de 32 bits, con un tamaño de página de 4 Kbytes = 2^12, se emplean 12 bits para el desplazamiento dentro de la página. Es decir, para referenciar los datos que una página contiene. Los restantes 20 bits más significativos indican el número de página.

El traductor de memoria paginada es parte de la arquitectura, por tanto, el sistema operativo únicamente tiene que establecer la tabla de páginas del proceso en tiempo de conmutación, de manera que cualquier acceso a una dirección lógica se traduce a una dirección física de una manera transparente al proceso.

Las páginas disponen de mecanismos de protección, expresados en bits de lectura, escritura y ejecución. Lo que permite definir páginas de sólo lectura, por ejemplo, para almacenar constantes. Páginas de sólo lectura y ejecución, para almacenar código, así como páginas de lectura y escritura para el heap (montón) o la pila (stack) del proceso.

Si se accede a una página lógica que no existe en la tabla de páginas del proceso, el sistema eleva una excepción que resulta en la finalización de la ejecución del proceso.

Otras características

- ¿Cuál es el tamaño de página idóneo? Los valores óptimos para las porciones son: en arquitectura de 32 bits es de 4KB, y en arquitectura de 64 bits es de 8KB.

- Los criterios vistos en la gestión de memoria mediante particiones de tamaño variable no tienen aplicación en la gestión de la memoria paginada, pues todos los huecos disponibles son de igual tamaño.

Dispositivo de traducción de direcciones paginadas

Podemos almacenar la tabla de páginas en el propio traductor o en memoria principal.

- Tabla de páginas en el traductor:

El dispositivo de traducción de memoria dispone de una zona en la que se almacena la tabla de páginas. En tiempo de conmutación, se tiene que copiar la tabla de páginas a memoria principal y se restaura la tabla de página del nuevo proceso que pasa a estado activo, lo cual ralentiza el tiempo de conmutación de procesos. Lo que hace que no sea viable en sistemas modernos, en los que se gestionan grandes cantidades de memoria.

- Tabla de páginas en memoria principal:

La tabla de página se almacena en la memoria principal, el dispositivo traductor dispone de unos registros que almacenan la dirección de memoria en la que se almacena la tabla de páginas y su tamaño. Debido a que la tabla de páginas está en la memoria principal se necesita, por cada acceso a memoria, un acceso a memoria adicional para obtener el número de página física asociado a la página lógica. Para mantener un tiempo de acceso aceptable se establece una memoria asociativa en el dispositivo de traducción de memoria paginada que conserva la relación página lógica <-> página física utilizadas recientemente.

Tabla de páginas multinivel

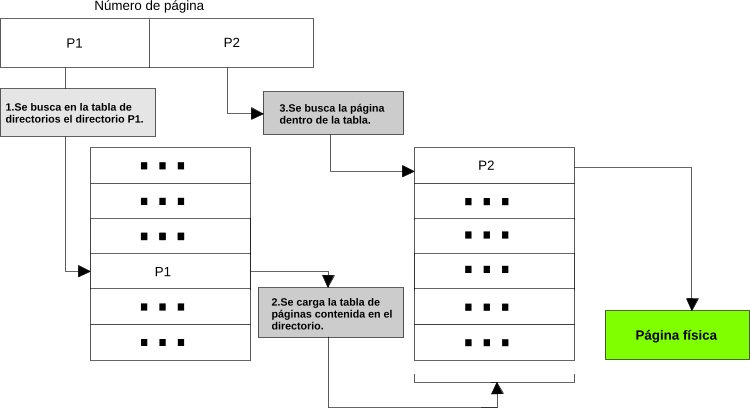

El objetivo es paginar la tabla de páginas lo que permite que esta no esté cargada completa en memoria y que no ocupe direcciones consecutivas. En los ss.oo. con tablas de páginas multinivel los números de página se dividen en dos partes: los bits más significativos indican el directorio de páginas correspondiente y con los bits menos significativos el índice del directorio en el que se encuentra la página buscada:

- Tabla de páginas para todo el sistema: Es una variante de las tablas de página multinivel, en la que el dispositivo traductor sólo contiene una entrada por cada proceso, indexadas por PID, y una dirección de tabla que contiene las páginas de dicho proceso. Así, ante una conmutación de procesos basta con cambiar de PID.

Elementos de administración

Para mantener la contabilidad de marcos libres se pueden emplear estructuras de datos tales como:

- Mapa de bits de marcos libres: Que contiene 1 si está asignada a un proceso, o 0 si está libre.

- Lista de marcos libres: Hay una lista global de marcos libres y una lista por proceso de marcos ocupados.

Además, se puede emplear el mecanismo de los compañeros para mantener listas de varias páginas consecutivas (bloques) de tamaño en base a potencia de 2. Por ejemplo, suponiendo un sistema con páginas de 4 Bytes, bloques de 4 Kbytes (orden 0), bloques de 8 Kbytes (orden 1, dos páginas), bloques de 16 Kbytes (orden 2, cuatro páginas), bloques de 32 KBytes (orden 3, 8 páginas) y así sucesivamente.

Una reserva de página de orden 0 nunca falla a no ser que no haya memoria disponible en el sistema. La de orden 1 puede fallar si no hay dos páginas consecutivas.

El hecho de asignar páginas de manera consecutiva permite explotar mejor la propiedad de localidad espacial en el acceso a memoria.